Thesys-Intechna provides standard & IO cell library development services at XFAB technology process nodes from 1 um to 0.18 um.

We have a wide experience in developing of digital and analog libraries with usage of energy-efficient engineering methods since 2003.

Digital library

- Basic components with optimized Speed/Power consumption/Size ratio and intended for designing of system-on-chip digital blocks operating at high frequency

- Components with optimized Power consumption/Size/Speed ratio and intended for designing of blocks with low consumption and lower operating frequency

- Components proving energy-efficient modes of system-on-chip operating: interaction of blocks with different voltage supplies, functioning and saving of information of blocks operating in standby mode with switched off power

Analog library

Analog libraries contain full information required for designing of analog and mixed-signal microcircuits in the various CADs. Simulation of cells parameters is carried out in parasitic capacities effect. After silicon implementation the parameters are characterized.

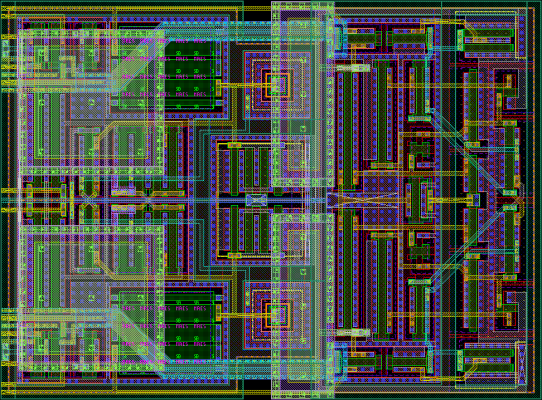

Design flow

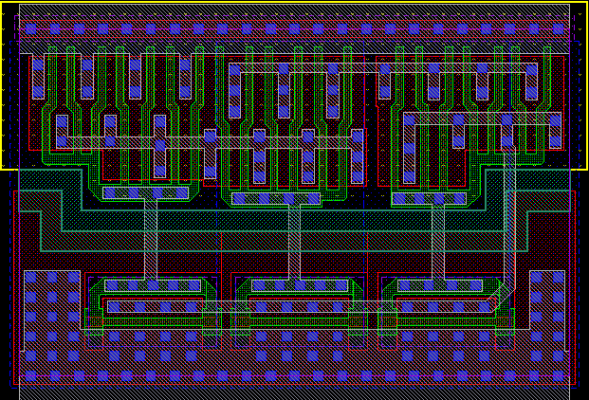

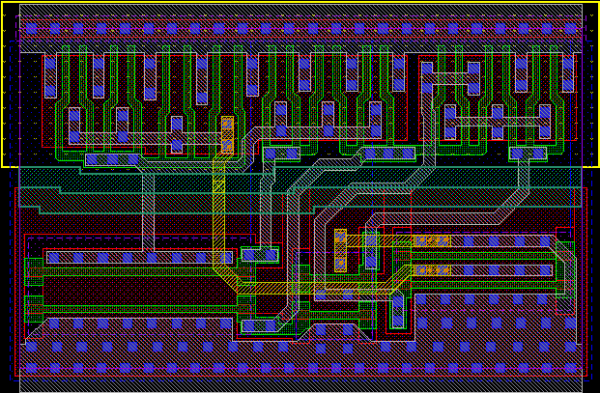

Search of design solutions providing high layout filled density

Optimization of operating modes and power consumption

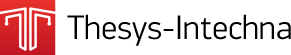

Layout design

Layout verification

Extraction of parasitic parameters of wiring

Generation of LEF files and Abstract views for automatic placement and wiring

Test chip development and manufacturing

Verification of the designed library

Layout correction

Library characterization

Specification development