# Thesys-Intechna

# FEATURES

- 12-bit resolution

- Sample rate: 20 MSPS

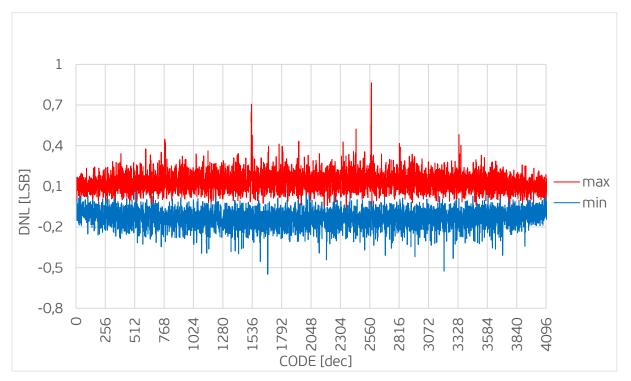

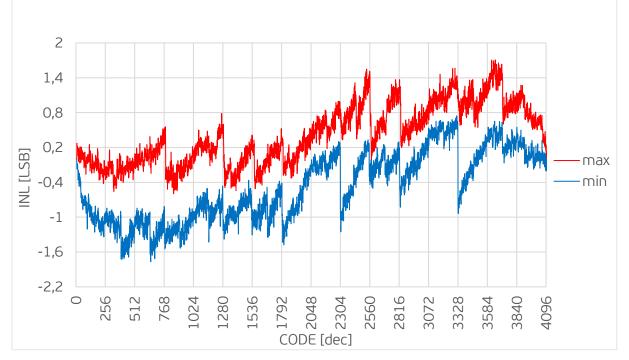

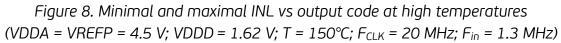

- INL: ±3 LSB

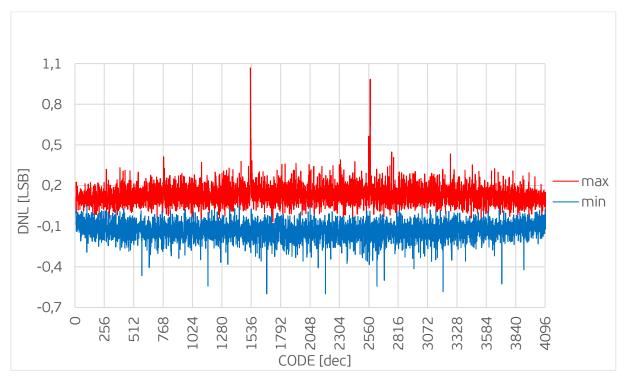

- DNL: ±0.8 LSB

- ENOB at 1.3 MHz input: 10.1 bits

### HIGHLIGHTS

- Fully differential architecture

- Integrated/external biasing choice

- Trimming mode of internal biasing

- Built-in calibration state machine for offset and gain calibration

- Built-in SPI for parameters tuning including Speed-to-Power Consumption ratio trimming

- Output clock for output data processing

- Separate analog and digital power supplies (5 V and 1.8 V correspondingly)

# 12-bit Pipeline ADC, 20 MSPS

# DATA SHEET

# TI-12PI/20M

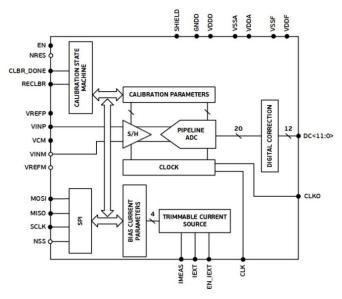

# FUNCTIONAL BLOCK DIAGRAM

# APPLICATIONS

- Space applications

- Communications

- SDR receivers

- Test and instrumentation

#### **GENERAL DESCRIPTION**

The TI-12PI/20M is a 12-bit analog-to-digital converter (ADC) with pipelined architecture and serial peripheral interface (SPI), which achieves conversion rate up to 20 MSPS. It has differential analog inputs and parallel data output. The device includes internal Sample & Hold (S&H) circuit, eight 1.5-bit stages, and one 4-bit Flash AD converter. Internal automatic prestart calibration system allows to tune consequently offset and gain of each pipeline stage using built-in analog calibration arrays for each parameter. Consequent calibration approach results in high static and dynamic parameters of the whole pipeline ADC system. The calibration module can be activated by power-on or by user. The SPI allows user to configure the following ADC parameters: biasing current, calibration coefficients of each stage, number of calibration iterations, delay between offset and gain calibrations.

User can make speed adjustment of operational amplifiers and comparators by adjusting internal current source or by using external current source for biasing. To increase speed, current should also be increased, but power consumption in this case rises as well. Thus, speed-to-power consumption ratio trimming is available.

# LIST OF CONTENTS

| Features                                      | 1  |

|-----------------------------------------------|----|

| Highlights                                    | 1  |

|                                               | 1  |

| Functional block diagram                      | T  |

| Applications                                  | 1  |

| General description                           | 1  |

| Device parameters                             | 3  |

| Pin functional description                    | 5  |

| Device operation                              | 6  |

| Memory map registers table                    | 9  |

| Internal current source                       | 11 |

| Requirements for power supply and ground nets | 12 |

| Requirements for external components          | 12 |

| Critical application notes                    | 12 |

| Typical performance characteristics           | 13 |

#### **DEVICE PARAMETERS**

VDDA = 4.5 to 5.5 V, VDDD = 1.62 to 1.98 V, VSSA = GNDD = 0 V; VREFP = VDDA, VREFM = 0, VCM = 0.5\*VDDA,  $F_{CLK}$  = 20 MHz, internal  $I_{BIAS}$  with default value (8), calibrated with internal routing, T = -40 to 150°C, unless otherwise noted

| Symbol                 | Parameter                            | Min                  | Тур              | Max             | Unit | Conditions and comments                 |  |  |  |  |

|------------------------|--------------------------------------|----------------------|------------------|-----------------|------|-----------------------------------------|--|--|--|--|

| Accuracy <sup>A)</sup> |                                      |                      |                  |                 |      |                                         |  |  |  |  |

| N                      | Resolution                           |                      | 12               |                 | Bits |                                         |  |  |  |  |

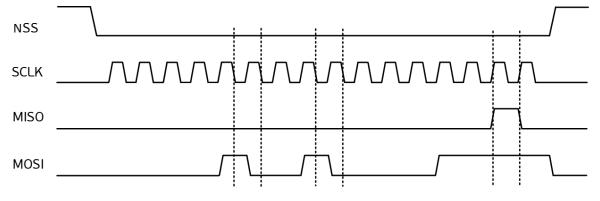

| INL                    | Integral nonlinearity                |                      | ±3.15            | ±3.31           | LSB  |                                         |  |  |  |  |

| DNL                    | Differential nonlinearity            |                      | ±0.86            | ±1.06           | LSB  | F <sub>in</sub> = 1.3 MHz sine<br>wave; |  |  |  |  |

| OE                     | Offset error                         |                      | ±0.68            | ±2.38           | LSB  | $F_{CLK} = 20 \text{ MHz}$              |  |  |  |  |

| GE                     | Gain error                           |                      | 0.99             | 1.00            | %    |                                         |  |  |  |  |

|                        | Dynamic pa                           | aramete              | rs <sup>A)</sup> |                 |      |                                         |  |  |  |  |

| ENOB                   | Effective number of bits             | 9.26                 | 9.93             | 10.10           | Bits |                                         |  |  |  |  |

| SNR                    | Signal-to-Noise ratio                | 59.9                 | 62.5             | 63.6            | dB   | F <sub>in</sub> = 1.3 MHz sine          |  |  |  |  |

| SINAD                  | Signal-to-Noise and distortion ratio | 57.5                 | 61.5             | 62.5            | dB   | wave;                                   |  |  |  |  |

| SFDR                   | Spurious-Free Dynamic Range          | 61.9                 | 68.8             | 70.75           | dB   | F <sub>CLK</sub> = 20 MHz               |  |  |  |  |

| THD                    | Total Harmonic Distortion            | 0.3                  | 0.4              | 0.8             | m%   |                                         |  |  |  |  |

|                        | Referen                              | ce inputs            | 5                |                 |      |                                         |  |  |  |  |

| VREFP                  | High reference voltage               | VCM+2                |                  | VDDA            | V    |                                         |  |  |  |  |

| VREFM                  | Low reference voltage                | VSSA                 |                  | VCM-2           | V    |                                         |  |  |  |  |

| VCM                    | Common mode voltage                  | 2                    | 2.5              | 3               | V    |                                         |  |  |  |  |

| CREFP                  | VREFP input capacitance              |                      | 15.4             |                 | рF   |                                         |  |  |  |  |

| CREFM                  | VREFM input capacitance              |                      | 17.7             |                 | рF   |                                         |  |  |  |  |

| Ссм                    | VCM input capacitance                |                      | 3.6              |                 | рF   |                                         |  |  |  |  |

| Irefp                  | Current through VREFP A)             | 1.95                 | 2.44             | 4.04            | mA   | Sourcing,<br>dynamic                    |  |  |  |  |

| Irefm                  | Current through VREFM <sup>A)</sup>  | 1.95                 | 2.44             | 4.04            | mA   | Sinking,<br>dynamic                     |  |  |  |  |

|                        | Analog                               | j inputs             |                  |                 |      |                                         |  |  |  |  |

|                        | Input voltage range                  | -(VREFP-<br>VREFM)   |                  | VREFP+<br>VREFM | V    | (VINP-VINM)                             |  |  |  |  |

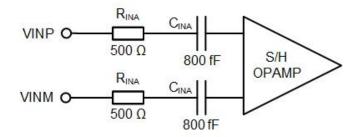

| Cina                   | Input capacitance <sup>B)</sup>      |                      | 800              |                 | fF   | VINP (VINM)                             |  |  |  |  |

| R <sub>INA</sub>       | Input resistance <sup>B)</sup>       | 500                  |                  | Ohm             |      |                                         |  |  |  |  |

|                        | Digital                              | inputs <sup>C)</sup> |                  |                 |      |                                         |  |  |  |  |

| VIH                    | Input high voltage level             | 1.4                  |                  |                 | V    |                                         |  |  |  |  |

| VIL                    | Input low voltage level              |                      |                  | 0.4             | V    |                                         |  |  |  |  |

| C <sub>EN</sub>        | Input capacitance of «EN»            |                      |                  | 96              | fF   |                                         |  |  |  |  |

#### **DEVICE PARAMETERS (continued)**

| Symbol               | Parameter                                              | Min              | Тур              | Max  | Unit    | Conditions and comments        |

|----------------------|--------------------------------------------------------|------------------|------------------|------|---------|--------------------------------|

| C <sub>EN_IEXT</sub> | Input capacitance of «EN_IEXT»                         |                  |                  | 76   | fF      |                                |

| C <sub>CLK</sub>     | Input capacitance of «CLK»                             |                  |                  | 832  | fF      |                                |

| CNRES                | Input capacitance of «NRES»                            |                  | 7                |      | рF      |                                |

| C <sub>MOSI</sub>    | Input capacitance of «MOSI»                            |                  | 136              |      | fF      |                                |

| C <sub>NSS</sub>     | Input capacitance of «NSS»                             |                  | 148              |      | fF      |                                |

| Csclk                | Input capacitance of «SCLK»                            |                  | 355              |      | fF      |                                |

| CRECLBR              | Input capacitance of «RECLBR»                          |                  | 178              |      | fF      |                                |

|                      | Digital                                                | outputs          |                  |      |         |                                |

| V <sub>OH</sub>      | Output high voltage level                              |                  |                  | VDDD | V       |                                |

| Vol                  | Output low voltage level                               | 0                |                  |      | V       |                                |

| CL                   | Load capacitance <sup>C)</sup>                         |                  | 500              |      | fF      | Rising/falling<br>edge is 2 ns |

|                      | Current cor                                            | sumptio          | <sup>A)</sup> חכ |      |         |                                |

| Idda                 | Analog part                                            | 27.4             | 33.8             | 44.2 | mA      |                                |

| Iddd                 | Digital part                                           | 1.2              | 1.2 3.8 4.3      |      |         | F <sub>CLK</sub> = 20 MHz      |

| Iddf                 | Clock module                                           | 3.8 4.4 4.9      |                  |      | mA      |                                |

|                      | Timi                                                   | ng <sup>C)</sup> |                  |      |         |                                |

| F <sub>CLK</sub>     | Clock frequency                                        |                  | 20               |      |         |                                |

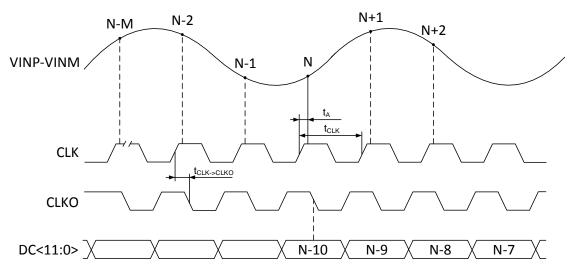

| tA                   | Aperture delay                                         | 2.8              | 3.7              | 6.1  | ns      |                                |

| tclk-clko            | CLK-CLKO delay                                         | 4.9              |                  |      | ns      |                                |

| tL                   | Pipeline latency                                       |                  | 7                |      | periods |                                |

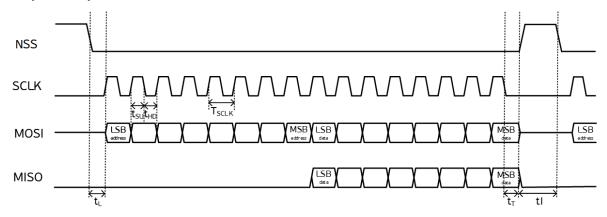

|                      | SPI ti                                                 | ming             | 1                | 1    |         |                                |

| Fsclk                | SPI clock frequency                                    |                  |                  | 20   | MHz     |                                |

| t <sub>su</sub>      | Setup time of data after a rising<br>edge of SPI clock | 25               |                  |      | ns      |                                |

| t <sub>HD</sub>      | Hold time of data after a falling<br>edge of SPI clock | 25               |                  |      | NS      |                                |

| tı                   | Leading time before the first SPI<br>clock edge        | 50               |                  |      | NS      |                                |

| t⊤                   | Trailing time after the last SPI clock edge            | 50               |                  |      | ΠS      |                                |

| tı                   | Idling time between transfers                          | 50               |                  |      | ns      |                                |

Notes:

<sup>A)</sup> Parameter is derived from measurements performed on 30 sampled devices from single wafer

<sup>B)</sup> Input resistance and input capacitance represent on-resistance of input switch and total capacitance of the Hold capacitor

<sup>C)</sup> Simulation results, 3-sigma statistical calculation

#### PIN FUNCTIONAL DESCRIPTION

| Pin name  | Description                        | Comments                                          |

|-----------|------------------------------------|---------------------------------------------------|

| EN        | Enable ADC                         | Active level - high                               |

| VREFP     | High reference voltage             |                                                   |

| VINP      | Analog input (+)                   |                                                   |

| VCM       | Common-mode voltage                |                                                   |

| VINM      | Analog input (-)                   |                                                   |

| VREFM     | Low reference voltage              |                                                   |

| EN_IEXT   | Enable external current source     | Active level – high, disables<br>internal biasing |

| CLK       | Clock input                        |                                                   |

| NRES      | Reset                              | Active level - low                                |

| MISO      | Master input slave output          |                                                   |

| MOSI      | Master output slave input          |                                                   |

| NSS       | Slave select                       | Active level – low                                |

| SCLK      | SPI input clock                    |                                                   |

| DC<11:0>  | Digital output data <11:0>         |                                                   |

| CLKO      | Clock output                       |                                                   |

| RECLBR    | Recalibration                      | Activates at falling edge                         |

| CLBR_DONE | "End of calibration" output signal | Active level - high                               |

| IMEAS     | Current measurement output         |                                                   |

| IEXT      | External current input             |                                                   |

| VDDF      | Clock module power supply          | Typical value: 5 V                                |

| VSSF      | Clock module ground                |                                                   |

| VDDA      | Analog power supply                | Typical value: 5 V                                |

| VSSA      | Analog ground                      |                                                   |

| VDDD      | Digital power supply               | Typical value: 1.8 V                              |

| GNDD      | Digital ground                     |                                                   |

| SHIELD    | Shield (ground)                    |                                                   |

#### TI-12PI/20M

#### **DEVICE OPERATION**

This analog-to-digital converter has pipelined architecture with internal Sample and Hold circuit. The input equivalent circuit is given in Figure 1.

Figure 1. Equivalent analog input circuit (during sampling phase)

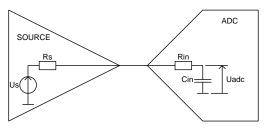

Input signal source output resistance must be also considered for proper sampling as shown in Figure 2.

Figure 2. Equivalent electrical circuit of signal source and ADC

The time constant of the circuit, to achieve an error less than 1/16LSB, is given by:

$$TC_{1/16LSB} = (R_{S} + R_{IN}) \times C_{IN} \times \ln 2^{(N+4)}$$

Where N is the resolution of the converter (in this case N=12).

The required input time constant must be small enough to be within the given ADC analog input sampling time. The acquisition for  $TC_{1/16LSB}$  should be used for calculation of maximum value of external driving source resistance to provide a desired ADC conversion accuracy.

The pipeline conversion core includes eight 1.5-bit stages and one 4-bit flash ADC. Every 1.5-bit stage receives an analog signal from the previous stage and produces output data that is sent further to the digital error-correction module.

S/H and every subsequent conversion stage have additional DACs for calibration of offset and gain of each stage. These DACs are controlled with stored register values. The process of data writing into the registers is performed by calibration state machine or by a user through SPI. In case of low «NSS» signal a user performs the process of data writing into all internal registers (not only calibration registers), otherwise the calibration is carried out automatically. During automatic calibration several iterations (256 iterations by default) with averaging are performed for the binary search of tuning coefficients. Approximate calibration time is calculated as follows:

$$t_{cal} \approx n_{iter} \times T_{CLK} \times n_{c/iter}$$

Where  $n_{iter}$  is the number of iterations and  $n_{c/iter}$  is the number of clock cycles per iteration.

At typical settings, the approximate time of calibration is 12.8 ms (~1000 clock cycles per iteration at 50 ns clock period). If recalibration is needed (for instance due to change in temperature), it can

be started by a pulse to «RECLBR». All the data of internal registers can be turned into default values via asserting «NRES» low.

Output data is valid for reading during falling edge of «CLKO». Latency of ADC is 7 input clock frequency periods. Sampling of the input signal is performed at the rising edge of «CLK» signal + aperture delay  $t_A$  (at the end of the sampling phase and the beginning of the hold phase).

Figure 3. Timing diagram

Input signal charges the hold capacitor in Sample-and-Hold circuit during sample phase (when «CLK» is low) and S/H holds the value of the input signal at the end of the sample phase (at the rising edge of «CLK» +  $t_A$ ).

Output data type is fully parallel.

The integrated SPI allows user to configure the ADC: biasing current, calibration coefficients of each stage, number of calibration iterations, delay between offset and gain calibrations.

The ADC's SPI operates as a slave relative to a user.

For reading or writing operation 16 bits should be transmitted to «MOSI». The first 8 bits is address (MSB defines reading if it is low and writing if it is high), and following 8 bits is data. The data in the SPI is latched at the falling edge of «SCLK». The transmitted data format is «LSB - first». Therefore, the reading/writing bit is the 8<sup>th</sup> bit in this chain.

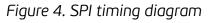

Figure 5. SPI example

On figure 5 there is an example of writing the data FO into a gain tuning coefficient for the S/H register (0x90). Simultaneously default data of the register is being transmitted from the ADC to «MISO».

#### MEMORY MAP REGISTERS TABLE

| Address | B7    | B6              | B5              | B4              | B3              | B2                     | B1              | BO              | Description                            |

|---------|-------|-----------------|-----------------|-----------------|-----------------|------------------------|-----------------|-----------------|----------------------------------------|

|         |       | 6 <sup>th</sup> | 5 <sup>th</sup> | 4 <sup>th</sup> | 3 <sup>rd</sup> | 2 <sup>nd</sup>        | 1 <sup>st</sup> | Oth             | Gain tuning coefficient for            |

| 0x00    | -     | bit             | bit             | bit             | bit             | bit                    | bit             | bit             | 1st stage (reading); default value: 40 |

|         |       | 6 <sup>th</sup> | 5 <sup>th</sup> | 4 <sup>th</sup> | 3 <sup>rd</sup> | 2 <sup>nd</sup>        | 1 <sup>st</sup> | Oth             | Gain tuning coefficient for            |

| 0x80    | -     | bit             | bit             | bit             | bit             | bit                    | bit             | bit             | 1st stage (writing)                    |

|         |       | 6 <sup>th</sup> | 5 <sup>th</sup> | 4 <sup>th</sup> | 3 <sup>rd</sup> | 2 <sup>nd</sup>        | 1 <sup>st</sup> | Oth             | Offset tuning coefficient for          |

| 0x01    | Sign  | bit             | bit             | bit             | bit             | bit                    | bit             | bit             | 1st stage (reading); default value: 0  |

|         |       | 6 <sup>th</sup> | 5 <sup>th</sup> | 4 <sup>th</sup> | 3 <sup>rd</sup> | 2 <sup>nd</sup>        | 1 <sup>st</sup> | Oth             | Offset tuning coefficient for          |

| 0x81    | Sign  | bit             | bit             | bit             | bit             | bit                    | bit             | bit             | 1st stage (writing)                    |

|         |       | 6 <sup>th</sup> | 5 <sup>th</sup> | 4 <sup>th</sup> | 3 <sup>rd</sup> | 2 <sup>nd</sup>        | 1 <sup>st</sup> | Oth             | Gain tuning coefficient for            |

| 0x02    | -     | bit             | bit             | bit             | bit             | bit                    | bit             | bit             | 2nd stage (reading); default value: 40 |

|         |       | 6 <sup>th</sup> | 5 <sup>th</sup> | 4 <sup>th</sup> | 3 <sup>rd</sup> | 2 <sup>nd</sup>        | 1 <sup>st</sup> | Oth             | Gain tuning coefficient for            |

| 0x82    | -     | bit             | bit             | bit             | bit             | bit                    | bit             | bit             | 2nd stage (writing)                    |

|         |       | 6 <sup>th</sup> | 5 <sup>th</sup> | 4 <sup>th</sup> | 3 <sup>rd</sup> | 2 <sup>nd</sup>        | 1 <sup>st</sup> | Oth             | Offset tuning coefficient for          |

| 0x03    | Sign  | bit             | bit             | bit             | bit             | bit                    | bit             | bit             | 2nd stage (reading); default value: 0  |

|         |       | 6 <sup>th</sup> | 5 <sup>th</sup> | 4 <sup>th</sup> | 3 <sup>rd</sup> | 2 <sup>nd</sup>        | 1 <sup>st</sup> | Oth             | Offset tuning coefficient for          |

| 0x83    | Sign  | bit             | bit             | bit             | bit             | bit                    | bit             | bit             | 2nd stage (writing)                    |

|         |       | 6 <sup>th</sup> | 5 <sup>th</sup> | 4 <sup>th</sup> | 3 <sup>rd</sup> | 2 <sup>nd</sup>        | 1 <sup>st</sup> | O <sup>th</sup> | Gain tuning coefficient for            |

| 0x04    | -     | bit             | bit             | bit             | bit             | bit                    | bit             | bit             | 3rd stage (reading); default value: 40 |

|         |       | 6 <sup>th</sup> | 5 <sup>th</sup> | 4 <sup>th</sup> | 3 <sup>rd</sup> | 2 <sup>nd</sup>        | 1 <sup>st</sup> | Oth             | Gain tuning coefficient for            |

| 0x84    | -     | bit             | bit             | 4<br>bit        | bit             | bit                    | bit             | bit             | 3rd stage (writing)                    |

|         |       | 6 <sup>th</sup> | 5 <sup>th</sup> | 4 <sup>th</sup> | 3 <sup>rd</sup> | 2 <sup>nd</sup>        | 1 <sup>st</sup> | Oth             | Offset tuning coefficient for          |

| 0x05    | Sign  | bit             | bit             | bit             | bit             | bit                    | bit             | bit             | 3rd stage (reading); default value: 0  |

|         |       | 6 <sup>th</sup> | 5 <sup>th</sup> | 4 <sup>th</sup> | 3 <sup>rd</sup> | 2 <sup>nd</sup>        | 1 <sup>st</sup> | O <sup>th</sup> | Offset tuning coefficient for          |

| 0x85    | Sign  | bit             | bit             | 4<br>bit        | bit             | bit                    | bit             | bit             | 3rd stage (writing)                    |

|         |       | 6 <sup>th</sup> | 5 <sup>th</sup> | 4 <sup>th</sup> | 3 <sup>rd</sup> | 2 <sup>nd</sup>        | 1 <sup>st</sup> | O <sup>th</sup> | Gain tuning coefficient for            |

| 0x06    | -     | bit             | bit             | bit             | bit             | bit                    | bit             | bit             | 4th stage (reading); default value: 40 |

|         |       | 6 <sup>th</sup> | 5 <sup>th</sup> | 4 <sup>th</sup> | 3 <sup>rd</sup> | 2 <sup>nd</sup>        | 1 <sup>st</sup> | O <sup>th</sup> | Gain tuning coefficient for            |

| 0x86    | -     | bit             | bit             | 4<br>bit        | bit             | bit                    | bit             | bit             | 4th stage (writing)                    |

|         |       | 6 <sup>th</sup> | 5 <sup>th</sup> | 4 <sup>th</sup> | 3 <sup>rd</sup> | 2 <sup>nd</sup>        | 1 <sup>st</sup> | O <sup>th</sup> | Offset tuning coefficient for          |

| 0x07    | Sign  | bit             | bit             | bit             | bit             | bit                    | bit             | bit             | 4th stage (reading); default value: 0  |

|         |       | 6 <sup>th</sup> | 5 <sup>th</sup> | 4 <sup>th</sup> | 3 <sup>rd</sup> | 2 <sup>nd</sup>        | 1 <sup>st</sup> | Oth             | Offset tuning coefficient for          |

| 0x87    | Sign  | bit             | bit             | bit             | bit             | bit                    | bit             | bit             | 4th stage (writing)                    |

|         |       | 6 <sup>th</sup> | 5 <sup>th</sup> | 4 <sup>th</sup> | 3 <sup>rd</sup> | 2 <sup>nd</sup>        | 1 <sup>st</sup> | O <sup>th</sup> | Gain tuning coefficient for            |

| 0x08    | -     | bit             | bit             | bit             | bit             | bit                    | bit             | bit             | 5th stage (reading); default value: 40 |

|         |       | 6 <sup>th</sup> | 5 <sup>th</sup> | 4 <sup>th</sup> | 3 <sup>rd</sup> | 2 <sup>nd</sup>        | 1 <sup>st</sup> | O <sup>th</sup> | Gain tuning coefficient for            |

| 0x88    | -     | bit             | bit             | bit             | bit             | bit                    | bit             | bit             | 5th stage (writing)                    |

|         |       | 6 <sup>th</sup> | 5 <sup>th</sup> | 4 <sup>th</sup> | 3 <sup>rd</sup> |                        | 1 <sup>st</sup> | O <sup>th</sup> |                                        |

| 0x09    | Sign  | -               | -               | -               | -               | 2 <sup>nd</sup><br>bit |                 | -               | Offset tuning coefficient for          |

|         |       | bit             | bit             | bit             | bit             |                        | bit             | bit             | 5th stage (reading); default value: 0  |

| 0x89    | Sign  | 6 <sup>th</sup> | 5 <sup>th</sup> | 4 <sup>th</sup> | 3 <sup>rd</sup> | 2 <sup>nd</sup>        | 1 <sup>st</sup> | O <sup>th</sup> | Offset tuning coefficient for          |

|         | _     | bit             | bit             | bit             | bit             | bit                    | bit             | bit             | 5th stage (writing)                    |

| OxOA    | -     | 6 <sup>th</sup> | 5 <sup>th</sup> | 4 <sup>th</sup> | 3 <sup>rd</sup> | 2 <sup>nd</sup>        | 1 <sup>st</sup> | O <sup>th</sup> | Gain tuning coefficient for            |

|         |       | bit             | bit             | bit             | bit             | bit                    | bit             | bit             | 6th stage (reading); default value: 40 |

| 0x8A    | -     | 6 <sup>th</sup> | 5 <sup>th</sup> | 4 <sup>th</sup> | 3 <sup>rd</sup> | 2 <sup>nd</sup>        | 1 <sup>st</sup> | O <sup>th</sup> | Gain tuning coefficient for            |

|         |       | bit             | bit             | bit             | bit             | bit                    | bit             | bit             | 6th stage (writing)                    |

| 0x0B    | Sign  | 6 <sup>th</sup> | 5 <sup>th</sup> | 4 <sup>th</sup> | 3 <sup>rd</sup> | 2 <sup>nd</sup>        | 1 <sup>st</sup> | 0 <sup>th</sup> | Offset tuning coefficient for          |

|         | Jigh  | bit             | bit             | bit             | bit             | bit                    | bit             | bit             | 6th stage (reading); default value: 0  |

| 0x8B    | Sign  | 6 <sup>th</sup> | 5 <sup>th</sup> | 4 <sup>th</sup> | 3 <sup>rd</sup> | 2 <sup>nd</sup>        | 1 <sup>st</sup> | O <sup>th</sup> | Offset tuning coefficient for          |

|         | 5.9.1 | bit             | bit             | bit             | bit             | bit                    | bit             | bit             | 6th stage (writing)                    |

## MEMORY MAP REGISTERS TABLE (continued)

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |                       | -               |                 |                 |                 | -               |                 | 1   |                                        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----------------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----|----------------------------------------|

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | OxOC  | _                     | 6 <sup>th</sup> | 5 <sup>th</sup> | 4 <sup>th</sup> | 3 <sup>rd</sup> | 2 <sup>nd</sup> | 1 <sup>st</sup> | Oth | -                                      |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0,000 |                       |                 |                 |                 |                 | bit             | bit             |     | 7th stage (reading); default value: 40 |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0.480 | 0.400                 | 6 <sup>th</sup> | 5 <sup>th</sup> | 4 <sup>th</sup> | 3 <sup>rd</sup> | 2 <sup>nd</sup> | 1 <sup>st</sup> | Oth | Gain tuning coefficient for            |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0,00  | _                     |                 |                 |                 |                 | bit             | bit             |     | 7th stage (writing)                    |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |       | Sign                  | 6 <sup>th</sup> | 5 <sup>th</sup> | 4 <sup>th</sup> | 3 <sup>rd</sup> | 2 <sup>nd</sup> | 1 <sup>st</sup> | Oth | Offset tuning coefficient for          |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | UXUD  | Sign                  | bit             | bit             | bit             | bit             | bit             | bit             | bit | 7th stage (reading); default value: 0  |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       | Cien                  | 6 <sup>th</sup> | 5 <sup>th</sup> | 4 <sup>th</sup> | 3 <sup>rd</sup> | 2 <sup>nd</sup> | 1 <sup>st</sup> | Oth | Offset tuning coefficient for          |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | UXOD  | Sign                  | bit             | bit             | bit             | bit             | bit             | bit             | bit | 7th stage (writing)                    |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0.00  |                       | 6 <sup>th</sup> | 5 <sup>th</sup> | 4 <sup>th</sup> | 3 <sup>rd</sup> | 2 <sup>nd</sup> | 1 <sup>st</sup> | Oth | Gain tuning coefficient for            |

| $0x8E$ -bitbitbitbitbitbitbitbitbitbit $0x0F$ Sign $6^{th}$ $5^{th}$ $4^{th}$ $3^{rd}$ $2^{nd}$ $1^{st}$ $0^{th}$ Offset tuning coefficient for $0x0F$ Sign $6^{th}$ $5^{th}$ $4^{th}$ $3^{rd}$ $2^{nd}$ $1^{st}$ $0^{th}$ Offset tuning coefficient for $0x8F$ Sign $6^{th}$ $5^{th}$ $4^{th}$ $3^{rd}$ $2^{nd}$ $1^{st}$ $0^{th}$ Offset tuning coefficient for $0x10$ - $6^{th}$ $5^{th}$ $4^{th}$ $3^{rd}$ $2^{nd}$ $1^{st}$ $0^{th}$ Gain tuning coefficient for $0x10$ - $6^{th}$ $5^{th}$ $4^{th}$ $3^{rd}$ $2^{nd}$ $1^{st}$ $0^{th}$ Gain tuning coefficient for $0x90$ - $6^{th}$ $5^{th}$ $4^{th}$ $3^{rd}$ $2^{nd}$ $1^{st}$ $0^{th}$ Gain tuning coefficient for $0x90$ - $6^{th}$ $5^{th}$ $4^{th}$ $3^{rd}$ $2^{nd}$ $1^{st}$ $0^{th}$ Offset tuning coefficient for $0x90$ - $6^{th}$ $5^{th}$ $4^{th}$ $3^{rd}$ $2^{nd}$ $1^{st}$ $0^{th}$ Offset tuning coefficient for $0x90$ - $6^{th}$ $5^{th}$ $4^{th}$ $3^{rd}$ $2^{nd}$ $1^{st}$ $0^{th}$ Offset tuning coefficient for $0x91$ Sign $6^{th}$ $5^{th}$ $4^{th}$ $3^{rd}$ $2^{nd}$ $1^{st}$ $0^{th}$ Intern | UXUE  | -                     | bit             | bit             | bit             | bit             | bit             | bit             | bit | 8th stage (reading); default value: 40 |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0.05  |                       | 6 <sup>th</sup> | 5 <sup>th</sup> | 4 <sup>th</sup> | 3 <sup>rd</sup> | 2 <sup>nd</sup> | 1 <sup>st</sup> | Oth | Gain tuning coefficient for            |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0x8E  | -                     | bit             | bit             | bit             | bit             | bit             | bit             | bit | 8th stage (writing)                    |

| $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0.05  | <i>c</i> :            | 6 <sup>th</sup> | 5 <sup>th</sup> | 4 <sup>th</sup> | 3 <sup>rd</sup> | 2 <sup>nd</sup> | 1 <sup>st</sup> | Oth | Offset tuning coefficient for          |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0x0F  | Sign                  | bit             | bit             | bit             | bit             | bit             | bit             | bit | 8th stage (reading); default value: 0  |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0.05  | <i>c</i> :            | 6 <sup>th</sup> | 5 <sup>th</sup> | 4 <sup>th</sup> | 3 <sup>rd</sup> | 2 <sup>nd</sup> | 1 <sup>st</sup> | Oth | Offset tuning coefficient for          |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0x8F  | Sign                  | bit             | bit             | bit             | bit             | bit             | bit             | bit | 8th stage (writing)                    |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0.10  |                       | 6 <sup>th</sup> | 5 <sup>th</sup> | 4 <sup>th</sup> | 3 <sup>rd</sup> | 2 <sup>nd</sup> | 1 <sup>st</sup> | Oth | Gain tuning coefficient for            |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0110  | -                     | bit             | bit             | bit             | bit             | bit             | bit             | bit | -                                      |

| bitbitbitbitbitbitbitbitbitbitbit $0x11$ Sign $6^{th}$ $5^{th}$ $4^{th}$ $3^{rd}$ $2^{nd}$ $1^{st}$ $0^{th}$ Offset tuning coefficient for $0x91$ Sign $6^{th}$ $5^{th}$ $4^{th}$ $3^{rd}$ $2^{nd}$ $1^{st}$ $0^{th}$ Offset tuning coefficient for $0x91$ Sign $6^{th}$ $5^{th}$ $4^{th}$ $3^{rd}$ $2^{nd}$ $1^{st}$ $0^{th}$ Offset tuning coefficient for $0x28$ $3^{rd}$ $2^{nd}$ $1^{st}$ $0^{th}$ Internal current source settings $0xA8$ $3^{rd}$ $2^{nd}$ $1^{st}$ $0^{th}$ Internal current source settings $0xA8$ $3^{rd}$ $2^{nd}$ $1^{st}$ $0^{th}$ Internal current source settings $0xA8$ $3^{rd}$ $2^{nd}$ $1^{st}$ $0^{th}$ Internal current source settings $0xA0$ $7^{th}$ $6^{th}$ $5^{th}$ $4^{th}$ $3^{rd}$ $2^{nd}$ $1^{st}$ $0^{th}$ Number of calibration iterations $0xA2$ $7^{th}$ $6^{th}$ $5^{th}$ $4^{th}$ $3^{rd}$ $2^{nd}$ $1^{st}$ $0^{th}$ Number of calibration iterations $0xA0$ bitbitbitbitbitbitbitbitbitbitsettings (or delay between $0xA2$ $7^{th}$                                                                                      | 0.00  |                       | 6 <sup>th</sup> | 5 <sup>th</sup> | 4 <sup>th</sup> | 3 <sup>rd</sup> | 2 <sup>nd</sup> | 1 <sup>st</sup> | Oth | Gain tuning coefficient for            |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0x90  | -                     | bit             | bit             | bit             | bit             | bit             | bit             | bit | S/H (writing)                          |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0.11  | <i>c</i> :            | 6 <sup>th</sup> | 5 <sup>th</sup> | 4 <sup>th</sup> | 3 <sup>rd</sup> | 2 <sup>nd</sup> | 1 <sup>st</sup> | Oth | Offset tuning coefficient for          |

| Ox91Signbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbitbit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | OXII  | Sign                  | bit             | bit             | bit             | bit             | bit             | bit             | bit | S/H (reading); default value: 0        |

| $Ox28$ $3^{rd}$ $2^{nd}$ $1^{st}$ $0^{th}$ Internal current source settings<br>(reading); default value: 8 $OxA8$ $3^{rd}$ $2^{nd}$ $1^{st}$ $0^{th}$ Internal current source settings<br>(reading); default value: 8 $OxA8$ $3^{rd}$ $2^{nd}$ $1^{st}$ $0^{th}$ Internal current source settings<br>(writing) $OxA8$ $3^{rd}$ $2^{nd}$ $1^{st}$ $0^{th}$ Internal current source settings<br>(writing) $Ox20$ $7^{th}$ $6^{th}$ $5^{th}$ $4^{th}$ $3^{rd}$ $2^{nd}$ $1^{st}$ $0^{th}$ Number of calibration iterations<br>settings (reading); default value: 2F $OxA0$ $7^{th}$ $6^{th}$ $5^{th}$ $4^{th}$ $3^{rd}$ $2^{nd}$ $1^{st}$ $0^{th}$ Number of calibration iterations<br>settings (writing) $OxA2$ $7^{th}$ $6^{th}$ $5^{th}$ $4^{th}$ $3^{rd}$ $2^{nd}$ $1^{st}$ $0^{th}$ Settings for delay between<br>calibration states (reading); default<br>value: 2 $OxA2$ $7^{th}$ $6^{th}$ $5^{th}$ $4^{th}$ $3^{rd}$ $2^{nd}$ $1^{st}$ $0^{th}$ Settings for delay between<br>calibration states (reading); default<br>value: 2                                              | 0.01  | <b>C</b> <sup>1</sup> | 6 <sup>th</sup> | 5 <sup>th</sup> | 4 <sup>th</sup> | 3 <sup>rd</sup> | 2 <sup>nd</sup> | 1 <sup>st</sup> | Oth | Offset tuning coefficient for          |

| Ox28<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0x91  | Sign                  | bit             | bit             | bit             | bit             | bit             | bit             | bit | S/H (writing)                          |

| OX28bitbitbitbitbit(reading); default value: 8OXA83rd2nd1stOthInternal current source settingsOXA83rd2nd1stOthInternal current source settingsOx207th6th5th4th3rd2nd1stOthNumber of calibration iterationsOx207th6th5th4th3rd2nd1stOthNumber of calibration iterationsOxA07th6th5th4th3rd2nd1stOthNumber of calibration iterationsOxA07th6th5th4th3rd2nd1stOthNumber of calibration iterationsOxA27th6th5th4th3rd2nd1stOthSettings for delay betweenOx227th6th5th4th3rd2nd1stOthSettings for delay betweenOx227th6th5th4th3rd2nd1stOthSettings for delay betweenOx227th6th5th4th3rd2nd1stOthSettings for delay betweenOx427th6th5th4th3rd2nd1stOthSettings for delay between                                                                                                                                                                                                                                                                                                                                                                                                      | 0.00  |                       |                 |                 |                 | 3 <sup>rd</sup> | 2 <sup>nd</sup> | 1 <sup>st</sup> | Oth | Internal current source settings       |

| OxA8bitbitbitbitbitwith our                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0x28  | -                     | -               | -               | -               | bit             | bit             | bit             | bit |                                        |

| OXA8bitbitbitbitbit(writing)Ox207th6th5th4th3rd2nd1stOthNumber of calibration iterations<br>settings (reading); default value: 2FOxA07th6th5th4th3rd2nd1stOthNumber of calibration iterations<br>settings (reading); default value: 2FOxA07th6th5th4th3rd2nd1stOthNumber of calibration iterations<br>settings (writing)OxA07th6th5th4th3rd2nd1stOthNumber of calibration iterations<br>settings (writing)Ox227th6th5th4th3rd2nd1stOthSettings for delay between<br>calibration states (reading); default<br>value: 2OxA27th6th5th4th3rd2nd1stOthSettings for delay between<br>calibration states (reading); default<br>value: 2                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0.40  |                       |                 |                 |                 | 3 <sup>rd</sup> | 2 <sup>nd</sup> | 1 <sup>st</sup> | Oth | Internal current source settings       |

| Ox20bitbitbitbitbitbitbitbitbitbitOxA07th6th5th4th3rd2nd1stOthNumber of calibration iterationsOxA07th6th5th4th3rd2nd1stOthNumber of calibration iterationsOxA07th6th5th4th3rd2nd1stOthSettings (writing)Ox227th6th5th4th3rd2nd1stOthSettings for delay between<br>calibration states (reading); default<br>value: 2Ox427th6th5th4th3rd2nd1stOthSettings for delay between<br>calibration states (reading); default<br>value: 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0xA8  | -                     | -               | -               | -               | bit             | bit             | bit             | bit |                                        |

| bitbitbitbitbitbitbitbitbitbitbitsettings (reading); default value: 2FOxAO7th6th5th4th3rd2nd1stOthNumber of calibration iterationsOxAObitbitbitbitbitbitbitbitbitsettings (writing)OxAO7th6th5th4th3rd2nd1stOthSettings for delay betweenOx227th6th5th4th3rd2nd1stOthSettings for delay betweenOxA27th6th5th4th3rd2nd1stOthSettings for delay betweenOxA27th6th5th4th3rd2nd1stOthSettings for delay between                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0.00  | 7 <sup>th</sup>       | 6 <sup>th</sup> | 5 <sup>th</sup> | 4 <sup>th</sup> | 3 <sup>rd</sup> | 2 <sup>nd</sup> | 1 <sup>st</sup> | Oth | Number of calibration iterations       |

| OxAObitbitbitbitbitbitbitbitbitbitbitOx227th6th5th4th3rd2nd1stOthSettings for delay between<br>calibration states (reading); default<br>value: 2OxA27th6th5th4th3rd2nd1stOth<br>bitSettings for delay between<br>calibration states (reading); default<br>value: 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0x20  | bit                   | bit             | bit             | bit             | bit             | bit             | bit             | bit | settings (reading); default value: 2F  |

| OxAObitbitbitbitbitbitbitbitbitbitbitsettings (writing)Ox227th6th5th4th3rd2nd1stOthSettings for delay between<br>calibration states (reading); default<br>value: 2OxA27th6th5th4th3rd2nd1stOthSettings for delay between<br>calibration states (reading); default<br>value: 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       | 7 <sup>th</sup>       | 6 <sup>th</sup> | 5 <sup>th</sup> | 4 <sup>th</sup> | 3 <sup>rd</sup> | 2 <sup>nd</sup> | 1 <sup>st</sup> | Oth | Number of calibration iterations       |

| Ox22 7 <sup>th</sup> 6 <sup>th</sup> 5 <sup>th</sup> 4 <sup>th</sup> 3 <sup>rd</sup> 2 <sup>nd</sup> 1 <sup>st</sup> 0 <sup>th</sup> Settings for delay between calibration states (reading); default value: 2   OxA2 7 <sup>th</sup> 6 <sup>th</sup> 5 <sup>th</sup> 4 <sup>th</sup> 3 <sup>rd</sup> 2 <sup>nd</sup> 1 <sup>st</sup> 0 <sup>th</sup> Settings for delay between calibration states (reading); default value: 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0xA0  | bit                   | bit             | bit             | bit             | bit             | bit             | bit             | bit |                                        |

| Ox227th6th5th4th3th2th1shOthcalibration states (reading); default<br>value: 2OxA27th6th5th4th3rd2nd1sh0thcalibration states (reading); default<br>value: 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |       | ⊐th                   | cth             | <b>c</b> th     | <b>a</b> th     | bac             | and             | <b>1</b> st     | oth |                                        |

| $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0x22  |                       | -               | -               | •               | -               | _               | -               | -   | , , , , , , , , , , , , , , , , , , ,  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |       | DIT                   | DIT             | DIT             | DIT             | DIT             | DIL             | DIT             | DIT | -                                      |

| VAAC bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0x42  | 7 <sup>th</sup>       | 6 <sup>th</sup> | 5 <sup>th</sup> | 4 <sup>th</sup> | 3 <sup>rd</sup> | 2 <sup>nd</sup> | 1 <sup>st</sup> | Oth |                                        |